| CSC258H5S Winter 2015 Midterm | Student Number: |

|-------------------------------|-----------------|

| Duration — 50 minutes         |                 |

| Last Name: KEY                | First Name:     |

Do **not** turn this page until you have received the signal to start. (Please fill out the identification section above and read the instructions below.)

Good Luck!

This midterm consists of 3 questions on 8 pages (including this one and two blank pages at the back). When you receive the signal to start, please make sure that your copy is complete.

Please write legibly and provide succinct, well-structured answers.

If you use any space for rough work, indicate clearly what you want marked. It is beneficial to show your work, so that we can interpret your answers and award partial credit.

If you are uncertain about how to answer a question, write down your assumptions and then solve the problem based on those assumptions.

If you wish to detach the final page of the test (the blank pages), you may. Be very sure to indicate if you want any part of the blank pages marked; otherwise, we will treat them as scrap paper.

# 1: \_\_\_\_\_/ 9 # 2: \_\_\_\_\_/ 6 # 3: \_\_\_\_\_/ 5

TOTAL: \_\_\_\_\_/20

# Question 1. Short Answer [9 MARKS]

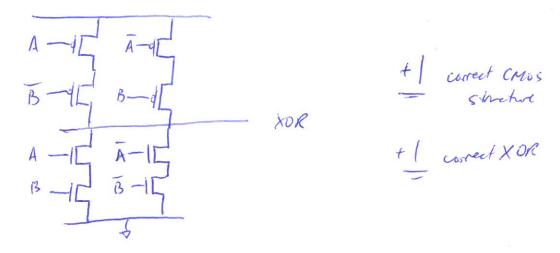

### Part (a) Transistors [2 MARKS]

Sketch a transistor-level circuit for a 2-input CMOS XOR gate. You may use A,  $\overline{A}$ , B, and  $\overline{B}$  as inputs to the transistors. (i.e., You don't need to implement a CMOS NOT gate.)

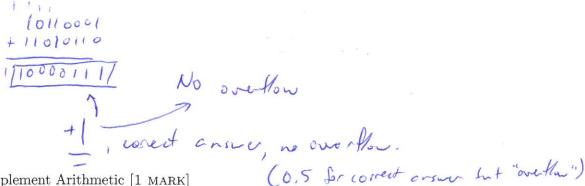

## Part (b) Two's Complement Arithmetic [1 MARK]

Showing your work, add 10110001 and 11010110. Indicate whether or not the sum overflows.

Part (c) Two's Complement Arithmetic [1 MARK]

Showing your work, subtract 00110001 from 10010110, Indicate whether or not the computation overflows.

00110001 =7

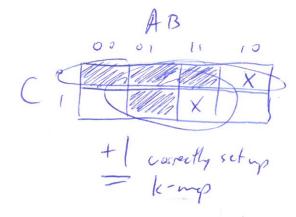

### Part (d) K-Maps [2 MARKS]

Use a Karnaugh map to simplify the function described in the truth table below. Provide the k-map and the optimized formula you derive from it.

| A | B | C | Out |

|---|---|---|-----|

| 0 | 0 | 0 | 1   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 1   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | X   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | X   |

C + B

+ 1 correctly extrated

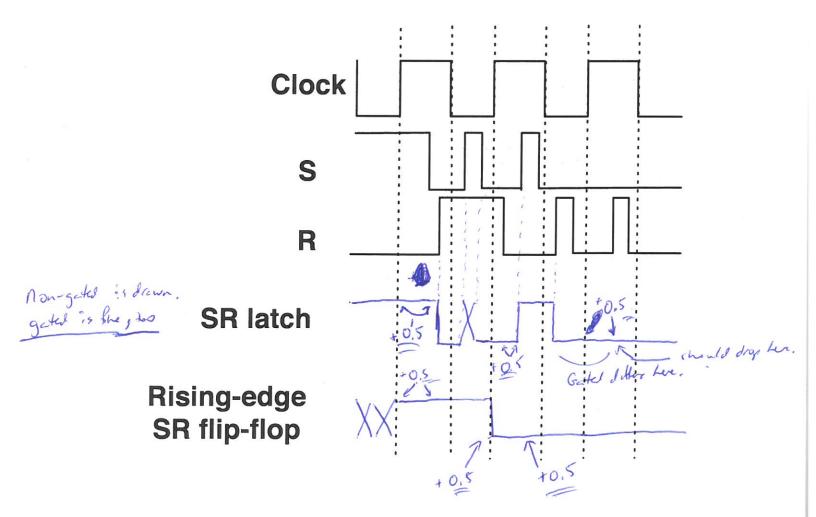

Part (e) Timing [3 MARKS]

Given the input waveform below, sketch the output, Q, of an SR latch and an SR flip-flop.

# Question 2. Circuit Analysis [6 MARKS]

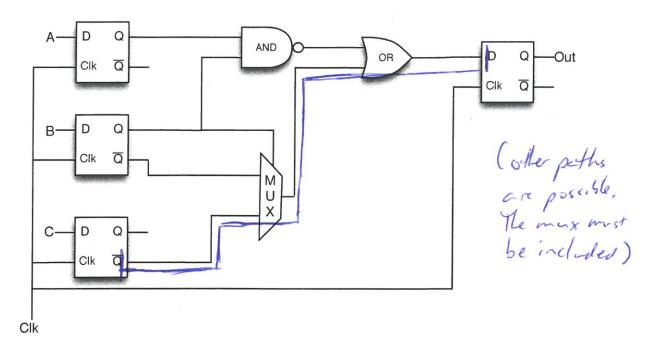

For the following subquestions, use the circuit above and assume that each 2-input boolean gate has a propagation delay of 30 ns and contamination delay of 15 ns. (NOT gates are free.) Assume that a D flip-flop has a clock-to-q propagation delay of 80 ns, setup time of 120 ns, hold time of 70 ns, and clock-to-q contamination delay of 40 ns.

Part (a) [2 MARKS] What are the propagation and contamination delays of the 2-1 multiplexer used in the circuit?

-

$$|x|$$

(a)  $|x|$  (b)  $|x|$   $|x|$

Part (b) [2 MARKS] What is the propagation delay of the full sequential circuit on the previous page? Please identify the longest path (by highlighting it on the circuit schematic) and show your work.

path: +1 prop delay: +1.

j-Afrection: +1

Part (c) [1 MARK] Does the circuit above contain a hold time violation? Explain why or why not.

Kold fine & Tacy + Top 70 < 40 + 2 × 15 No violetion. 70 < 70 Short-path Delay is egood to hold time.

Part (d) [1 MARK] This circuit has a simpler representation. Provide a simpler boolean formula for the combinational portion of the circuit. Show the work you performed to arrive at the simpler circuit.

The max can be real in two weys. Assuring the top imput 01 0 AB + (BB + BC) => A+B+B+BC If the ty input is selected on a 1: AB+ (BB+BC) => A+B+BC 0 01 11 10 2 1 1 1 1 3 A+B

Page 5 of 8

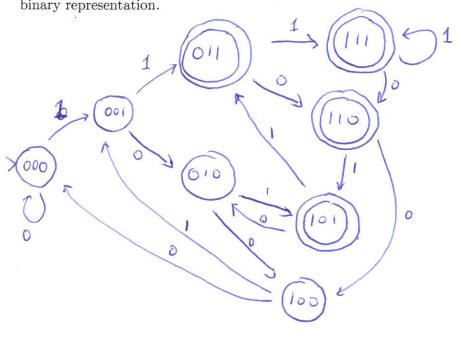

# Question 3. Finite State Machines [5 MARKS]

In this problem, you will be exploring the design of a FSM with two inputs - A and a clock - and one output - alert. alert should be 1 if A has been 1 in at least two of the previous three cycles.

Part (a) [3 MARKS] Draw the Moore state transition diagram for this FSM. Label each state with its

binary representation.

Clock is implied. Each transfor ours on the clarkedge. Alert is I in accepting (double circle) states.

+1 true-based structure

+1 "alert" correctly set

+1 transitions on "A"

[2 MARKS] Provide the state transition table and output table for this FSM.

|       | ( - ( - ) | it is a |       | casic and carp |

|-------|-----------|---------|-------|----------------|

| State | A         | 1 state | -1/-  | 1 alert        |

| 000   | 0         | 000     | State | alo            |

| 000   | ţ         | 001     | 000   | 0              |

| 001   | 0         | 010     | 001   | 0              |

| 001   | 1         | 011     | 010   | 0              |

| 010   | 0         | 100     | 011   | 1              |

| 010   | (         | 101     | 100   | O              |

| 0 11  | 0         | 110     | 101   | 1              |

| 011   | 1         | 121     | (1)   | 1              |

| 100   | 0         | 000     |       |                |

| 100   | ( )       | 001     |       |                |

| 101   | 0         | 010     |       |                |

| 101   | . 1       | 011     |       |                |

| 110   | O         | 100     |       |                |

| 110   | 1         | 101     |       |                |

| 111   | 0         | 110     |       |                |

| ili   | 1         | 111     | -     |                |

t | transition testenables

(a)

t | eintput teste actiles

(c), is moore